- 5/5A low-overhead Monitoring Ring Interconnect for MPSoC Parameter Optimization. 15th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems (DDECS), IEEE, 2012, 46-49 mehr… BibTeX

- 4/5An architecture and an FPGA prototype of a Reliable Processor Pipeline towards multiple soft- and timing errors. 14th IEEE Symposium on Design and Diagnostics of Electronic Circuits and Systems, 2011 mehr… BibTeX

- 3/5A Rapid Prototyping System for Error-Resilient Multi-Processor Systems-on-Chip. DATE Conference, 2010 mehr… BibTeX

- 2/5A Fault-Tolerant Processor Architecture. Workshop „Dependability and Fault-Tolerance“ (ARCS), 2009 mehr… BibTeX

- 1/5Multi-Bit Error Protection for Self-Correcting CPU Pipelines. eda Workshop, 2009 mehr… BibTeX

AIS - Autonomic Integrated Systems

Motivation and Targets

Due to CMOS devices downscaling, reliability is a new integrated circuit design parameter to consider in addition to classical power/performance/area design parameters.

Reliability has been considered in critical applications (military, space...). Due to CMOS technology evolution, reliability must be considered even in consumer electronics. New techniques have to be developed because the high overheads that can be tolerated in critical applications are not accepted in other applications.

AIS aims to define new low-overhead architectures for processor datapath hardening. This architectures address single and multiple soft- and timing errors.

Approach and Results

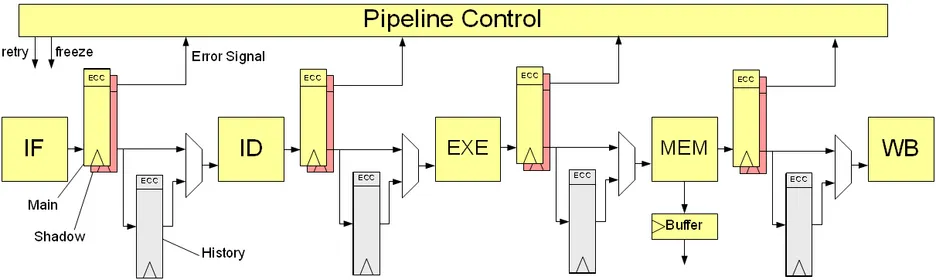

In order to select the wise transient and timing errors monitors, a fault model has to be chosen. SEU, SET and timing fault models are presented in [VTS99]. We introduced an extension towards multiple SEU, SET and timing errors in [edaworkshop09]. Based on this multiple transient and timing error monitors, we build a micro-rollback based reliable processors. Each single/multiple error is corrected within a penalty of two clock cycles. The architecture of this reliable processor is in the figure below.

This reliable architecture has been implemented in a Leon3 processor pipeline. An FPGA protoype has also been developed in a Virtex4 FPGA based board.