CeCaS

Mannheim CeCaS is a supra-regional research project funded by the BMBF to develop a "Central Car Server" for future automated, connected and electrified vehicles. The project network consists of numerous industrial partners, accompanied by several academic research groups.

Overarching Objective: Automotive Supercomputing Platform - powerful Central Car Server concept based on new automotive qualified high performance processors, in FinFET supported by application specific accelerators and adaptive automotive SW stack for highly automated connected vehicles.

At the Technical University of Munich, three chairs (TUM-AIR, TUM-LIS, TUM-SEC) are involved in the CeCaS project network, contributing in the areas of model-based development, requirements management, software architecture, memory technology, and security.

Contribution of LIS

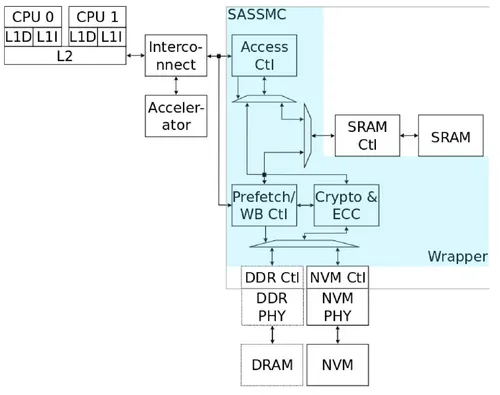

TUM-LIS is developing approaches for intelligent pre-fetching and write-back of data by the memory controller to increase the performance of the automotive processor. In addition, a prediction model for future addresses and data accesses is being investigated using machine learning methods such as reinforcement learning.

The current approach provides a wrapper layer around the DDR controller that realizes this functionality. It reduces the access latencies to external volatile and non-volatile main memories via adaptive prefetching of data and instructions in fast on-chip SRAM memories and by intelligent write-back of modified data located in the SRAM memory to the external main memory.

In the work on the wrapper layer we cooperate with TUM-SEC who investigate suitable lightweight techniques for transparent on-the-fly en-/de-cryption of data stored on external memory to prevent unauthorized access as well as error correction codes.

Workflow

In the CeCaS project we take a two-sided approach. On the one hand, we examine various implementation concepts and approaches with a SystemC based simulation model together with our partners. On the other hand, we are also working on an FPGA implementation, which offers a deeper level of abstraction for even more precise analyses. In both areas there are often topics for student work.

Involved Researchers

Open Student Work

Current Student Work

Generischer AXI-Traffic-Analyser zur Charakterisierung von Speicher- und Buszugriffen in eingebetteten Systemen

Beschreibung

Ziel dieser Bachelorarbeit ist die Konzeption und prototypische Umsetzung eines generischen AXI-Traffic-Analysers, der an beliebigen Stellen eines Systems mit AXI-Interface instanziiert werden kann. Der Analyser soll es ermöglichen, den Datenverkehr auf dem Bus flexibel an unterschiedlichen Beobachtungspunkten zu erfassen und auszuwerten. Damit soll eine wiederverwendbare Hardware-Komponente entstehen, die zur Charakterisierung von Kommunikations- und Speicherzugriffsmustern eingesetzt werden kann.

Neben klassischen Kenngrößen wie Datenrate, Zugriffsrate oder Verhältnis von Lese- und Schreibzugriffen sollen insbesondere weiterführende Metriken zur Beschreibung des Zugriffsverhaltens untersucht und implementiert werden. Dazu gehören unter anderem die Verteilung von Strides zwischen aufeinanderfolgenden Speicherzugriffen, die Stabilität dieser Strides über die Zeit, die Dominanz bzw. Verteilung einzelner Cores oder Initiatoren auf dem Bus sowie die Abschätzung des aktuellen Working Sets, beispielsweise über die Anzahl gleichzeitig genutzter Speicherseiten. Darüber hinaus soll analysiert werden, ob ein beobachtetes System eher konstantes oder stark schwankendes Zugriffsverhalten aufweist.

Der AXI-Traffic-Analyser soll zunächst so ausgelegt werden, dass seine Messdaten über den Bus ausgelesen werden können. Bereits bei der Architektur und Schnittstellendefinition soll jedoch eine spätere Erweiterung hin zu einer non-intrusiven Ethernet-Streaming-Variante berücksichtigt werden. Perspektivisch soll der Analysator somit nicht nur lokal auslesbare Statistiken bereitstellen, sondern auch eine kontinuierliche Übertragung von Messdaten über Ethernet unterstützen, sobald ein entsprechendes Interface im Gesamtsystem verfügbar ist.

Im Rahmen der Arbeit sollen die Anforderungen an einen solchen Analysator definiert, eine Hardware-Architektur entworfen und ein erster Prototyp implementiert sowie beispielhaft evaluiert werden.

Voraussetzungen

- Good Knowledge about MPSoCs

- Good C programming skills

- Very good VHDL programming skills

- High motivation

- Self-responsible workstyle

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Evaluation of a Page-Based Memory Preload Architecture Using Standardized Embedded Benchmarks

Beschreibung

Modern MPSoC architectures are increasingly limited by off-chip memory latency. To mitigate this bottleneck, a page-based hardware preload unit has been developed that speculatively transfers DRAM pages upon last-level cache misses in order to hide memory access latency.

The goal of this bachelor thesis is to perform a systematic and scientifically sound evaluation of this architecture using internationally recognized embedded benchmark suites. The work will focus on identifying, porting, and executing suitable bare-metal benchmarks on an FPGA-based RISC-V platform (CVA6 architecture). Candidate benchmark suites include Embench, CoreMark, PolyBench/C, MiBench, and other memory-intensive workloads. The final selection will be made during the course of the thesis based on feasibility and relevance.

The thesis involves implementing the benchmarks in the existing hardware/software framework, conducting structured performance measurements, and comparing different system configurations (e.g., with and without the preload unit). Particular emphasis will be placed on analyzing memory behavior, working-set characteristics, and access patterns.

Beyond implementation, the thesis will provide a scientific evaluation of how different workload classes interact with page-based preloading. Results will be analyzed quantitatively and presented in a clear and reproducible manner using normalized speedups and workload classifications.

The outcome of this work will provide a solid experimental foundation for further research and potential publications in the area of memory-optimized MPSoC architectures.

Voraussetzungen

- Good Knowledge about MPSoCs

- Good C programming skills

- Basic understanding of hardware-oriented programming style

- High motivation

- Self-responsible workstyle

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Balancing Preload Efficiency and Responsiveness through Adaptive Burst Lengths

Beschreibung

Page-based memory preloading typically relies on fixed burst lengths to transfer data efficiently from DRAM. While long bursts maximize preload throughput, they reduce responsiveness to demand-driven CPU memory accesses. Short bursts improve reactivity but underutilize available memory bandwidth.

This thesis builds on the existing page-based preload unit and investigates a hardware-based mechanism for dynamically adjusting preload burst length according to current memory system utilization. The goal is to balance preload efficiency and fast reaction to demand accesses at runtime. The proposed mechanism adapts burst length based on simple runtime indicators such as DRAM activity or the presence of competing CPU requests. The implementation extends the existing preload FSM and does not require any modifications to the CPU microarchitecture

Evaluation on an FPGA-based platform analyzes execution time, interference with demand accesses, and bandwidth utilization under different memory-intensive workloads. The results aim to demonstrate that adaptive burst sizing is an effective and low-overhead technique to improve the robustness of memory-side preloading.

Voraussetzungen

- Good Knowledge about MPSoCs

- Good C programming skills

- High motivation

- Self-responsible workstyle

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Completed Student Work

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de

Betreuer:

Student

Betreuer:

Student

Kontakt

Oliver Lenke

o.lenke@tum.de