Motivation & Overview

In today's interconnected world, reliable high-performance transaction and smart contract systems are becoming increasingly important due to potentially distrustful stakeholders. The ACE-SUPPRA project is conducting Security, Usability, Performance, and Privacy Research on the Algorand protocol, a promising platform for future blockchain systems due to its Proof-of-Stake (PoS)-based design and powerful smart contract language. ACE-SUPPRA is addressing various challenges of upcoming blockchain networks and investivating new concepts and possibilities to improve the properties implied by its name. Funded by the Algorand Foundation, it is part of the Algorand Centers of Excellence (ACE) program, and encompasses five chairs at TUM, jointly working on the project.

- Chair of Network Architectures and Services (NET) of Prof. Dr.-Ing. Georg Carle

- Chair of Integrated Systems (LIS) of Prof. Dr. sc. techn. Andreas Herkersdorf

- Chair for Software and Systems Engineering (SSE) of Prof. Dr. Alexander Pretschner

- Chair for Software Engineering for Business Information Systems (SEBIS), of Prof. Dr. Florian Matthes

- Chair for Strategy and Organization (SAO) of Prof. Dr. Isabell Welpe

Research Focus

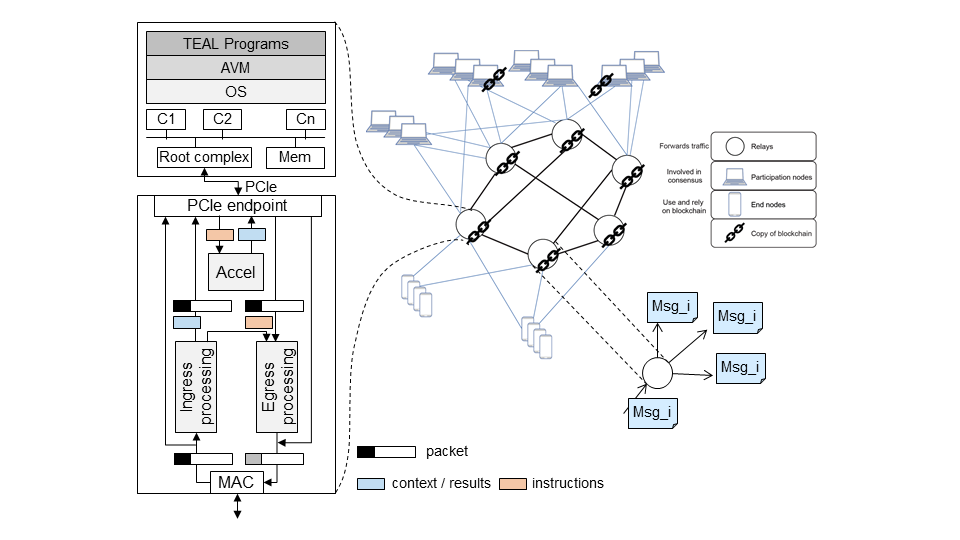

At LIS, we are focussing on the development and the evaluation of performance enhancements by increasing the throughput and reducing the latency in the system. Our approach to achive these goals is the development of new SmartNIC solutions to which certain operations can be offloaded. The performance and scalability of the Algorand protocol to a large extent depend on the message processing and forwarding capabilities of relay nodes which we aim to improve using SmartNIC-based hardware accelerators.