- 5/5Virtual Platforms: Breaking New Grounds. Design, Automation and Test in Europe Conference (DATE), 2012 more… BibTeX

- 4/5System-level Software Performance Simulation Considering Out-of-order Processor Execution. International Symposium on System-on-Chip, 2012 more… BibTeX

- 3/5Context-aware compiled simulation of out-of-order processor behavior based on atomic traces. 19th IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), 2011 more… BibTeX

- 2/5High-level timing analysis of concurrent applications on MPSoC platforms using memory-aware trace-driven simulations. 18th IEEE/IFIP International Conference on VLSI and System-on-Chip (VLSI-SoC), 2010 more… BibTeX

- 1/5A Method for Accurate High-Level Performance Evaluation of MPSoC Architectures using Fine-Grained Generated Traces. International Conference on Architecture of Computing Systems (ARCS), 2010 more… BibTeX

McSIM - Trace-driven simulator for multiprocessor systems-on-chip

Motivation and Targets

During system-level design of Multiprocessor Systems-on-Chip (MPSoCs), designers are faced with a problem of finding a suitable architecture that would fulfil the requirements of applications while minimizing hardware costs. A typical design flow involves modeling and simulation of diverese candidate architectures at the system level. Cycle-accurate processor models, e.g. instruction set simulators, cannot be employed at this level because of their high complexity and low simulation perfomance. In order to speed up the evaluation, designers require tools for design space exploration of MPSoCs at a higher level of abstraction.

Approach and results

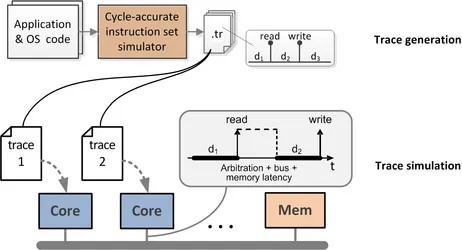

Trace-driven simulation (TDS) is a technique for performance estimation of MPSoC architectures. The purpose of this approach is to speed up the performance simulations by eliminating unnecessary internal events of a processor (intra-core events) and focusing on system-level (or inter-core) events only. A trace is a sequence of system-level events generated by the cycle-accurate processor model. Traces represent the abstracted behaviour of processors at the system level. During TDS, the traces of multiple processors are simulated using a trace-driven model of MPSoC, allowing the designer to investigate the impact of shared resources on the performance characteristics of the architecture candidates.

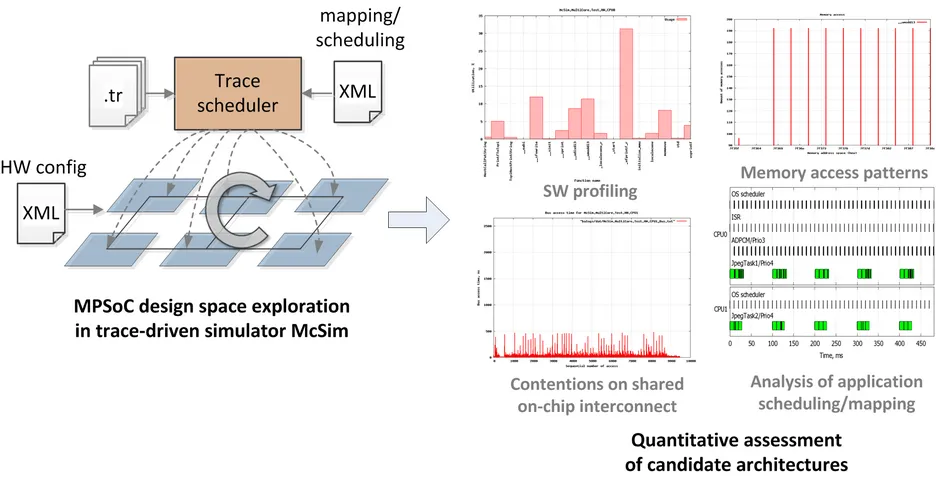

Traces are reused multiple times during design space exploration, avoiding slow microarchitecture simulations at each iteration. The presented approach can be applied for the high-level analysis of application mapping and scheduling. By means of a high-level scheduler, application traces can be dynamically mapped and executed on the MPSoC model, providing the designer with early estimates of the application performance on different candidate architectures considering features of real-time operating systems.

Past cooperations