Hardware Implementations

Contact: Patrick Karl, Jens Nöpel

Cryptographic Accelerators

Cryptographic workloads are highly compute-intensive and often latency-sensitive, requiring significant processing power and fast response times to meet security and performance demands. Leveraging hardware acceleration can substantially improve performance, reduce latency, and enhance energy efficiency, making it a key enabler for high-speed, secure systems.

A key challenge lies in balancing performance, latency, and flexibility. While dedicated hardware accelerators offer high throughput and low latency, they can lack adaptability for evolving cryptographic algorithms or variable workloads. Furthermore, different design integration approaches, such as tightly coupled versus loosely coupled architectures, present trade-offs in terms of scalability, programmability, and overall system complexity.

Our work focuses on designing and implementing hardware acceleration for cryptographic algorithms that balance high performance with flexibility. We target symmetric algorithms to enhance memory security, providing low-latency protection of data during operation. Memory security is particularly critical for safeguarding sensitive information against physical attacks, cold-boot attacks, and unauthorized memory access in modern computing systems.

In addition, we explore post-quantum cryptography (PQC) implementations, developing hardware-efficient architectures that can support emerging standards and ensure long-term security against quantum-enabled threats.

Chip Design

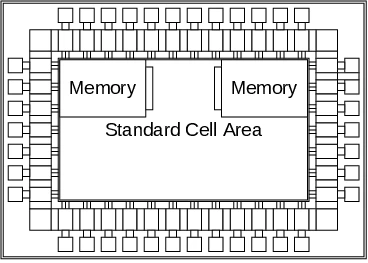

Early stage testing of hardware implementations is typically conducted on FPGA devices for fast prototyping. However, at our chair we also build actual chips that contain our developed hardware architectures and accelerators. So far we have integrated these accelerators on RISC-V based microcontroller platforms and designed chips in 65nm and 22nm technologies. Whereas the focus on the 65nm designed was low-power and energy efficiency, the 22nm was targeting high-performance designs.

Designing ASICs not only comprises frontend RTL design and synthesis, but also the whole backend chain including manual floorplanning, power-planning as well as layouting and DRC checking.

Building our own chips enables us to test and measure our designs on real silicon to investigate effects that are not necessarily measurable on FPGAs due to their inherent architectural differences.

Courses

Interested students are encouraged to participate in the study program Microelectronics and Chip Design

Selected Publications

Patrick Karl, Francesco Antognazza, Alessandro Barenghi, Gerardo Pelosi, Georg Sigl:

High-Performance FPGA Accelerator for the Post-quantum Signature Scheme CROSS. IACR Cryptol. ePrint Arch. 2025: 1161 (2025)

J. Schupp, P. Karl, J. Nöpel, A. Hepp, T. Music and G. Sigl, "RISC-V Triplet: Tapeouts for Security Applications," 2024 IEEE Nordic Circuits and Systems Conference (NorCAS), Lund, Sweden, 2024, pp. 1-6, doi: 10.1109/NorCAS64408.2024.10752453.

Patrick Karl, Jonas Schupp, Georg Sigl:

The Impact of Hash Primitives and Communication Overhead for Hardware-Accelerated SPHINCS+. COSADE 2024: 221-239

Patrick Karl, Jonas Schupp, Tim Fritzmann, Georg Sigl:

Post-Quantum Signatures on RISC-V with Hardware Acceleration. ACM Trans. Embed. Comput. Syst. 23(2): 30:1-30:23 (2024)

Tim Fritzmann, Michiel Van Beirendonck, Debapriya Basu Roy, Patrick Karl, Thomas Schamberger, Ingrid Verbauwhede, Georg Sigl:

Masked Accelerators and Instruction Set Extensions for Post-Quantum Cryptography. IACR Trans. Cryptogr. Hardw. Embed. Syst. 2022(1): 414-460 (2022)