2025

Zeitschriftenartikel

- Bandwidth and Crosstalk Optimisation for Wavelength-Routed Optical Networks-on-Chip using Pareto Simulated Annealing. IEEE/OSA Journal of Lightwave Technology (JLT), 2025 mehr… BibTeXWWW

- ToPro+: A Topology Projector Considering Port Assignment and Waveguide Routing for Wavelength-Routed Optical Networks-on-Chip. IEEE/OSA Journal of Optical Communications and Networking (JOCN) 17 (7), 2025, 601-615 mehr… BibTeXWWW

Konferenzbeiträge / Poster

- CPONoC: Critical Path-aware Physical Implementation for Optical Networks-on-Chip. IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC), 2025 mehr… BibTeX Volltext (mediaTUM)

- Process-Variation-Aware Design Optimization for Wavelength-Routed Optical Networks-on-Chip. ACM/IEEE Design Automation Conference (DAC), 2025 mehr… BibTeX Volltext (mediaTUM)

- A Backup Resource Customization and Allocation Method for Wavelength-Routed Optical Networks-on-Chip Topologies. IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC), 2025 mehr… BibTeX Volltext (mediaTUM)

- A Lifetime Extension Framework for Communication-Intensive Systems Based on Wavelength-Routed Optical Networks-on-Chip. ACM Great Lakes Symposium on VLSI (GLSVLSI), 2025 mehr… BibTeX Volltext (mediaTUM)

- SRing: A Sub-Ring Construction Method for Application-Specific Wavelength-Routed Optical NoCs. Design, Automation and Test in Europe (DATE), 2025 mehr… BibTeX Volltext (mediaTUM)

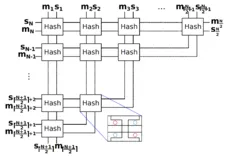

- Accurate Fault Detection for Wavelength-Routed Optical Networks-on-Chip Under Thermal Variation. ACM Great Lakes Symposium on VLSI (GLSVLSI), 2025 mehr… BibTeX Volltext (mediaTUM)

2024

Konferenzbeiträge / Poster

- Minimizing Worst-Case Data Transmission Cycles in Wavelength-Routed Optical NoC through Bandwidth Allocation. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2024 mehr… BibTeX Volltext (mediaTUM)

- Multi-Resonance Mesh-Based Wavelength-Routed Optical Networks-on-Chip. ACM/IEEE Design Automation Conference (DAC), 2024 mehr… BibTeX Volltext (mediaTUM)

2023

Zeitschriftenartikel

- Accurate Infinite-order Crosstalk Calculation for Optical Networks-on-Chip. IEEE/OSA Journal of Lightwave Technology (JLT) 41 (1), 2023, 4 - 16 mehr… BibTeX Volltext ( DOI ) Volltext (mediaTUM)

- LightR: A Fault-Tolerant Wavelength-Routed Optical Networks-on-Chip Topology. MDPI Applied Sciences 13 (15), 2023, 8871 mehr… BibTeX Volltext ( DOI ) WWW

Konferenzbeiträge / Poster

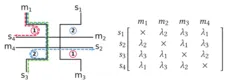

- XRing: A Crosstalk-Aware Synthesis Method for Wavelength-Routed Optical Ring Routers. Design, Automation and Test in Europe (DATE), 2023 mehr… BibTeX Volltext (mediaTUM)

2022

Zeitschriftenartikel

- Crosstalk-Aware Automatic Topology Customization and Optimization for Wavelength-Routed Optical NoCs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD) 41 (12), 2022, 5261 - 5274 mehr… BibTeX Volltext (mediaTUM)

2021

Bücher / Beiträge zu Sammelbänden

- Efficiency-Oriented Design Automation Methods for Wavelength-Routed Optical Network-on-Chip. In: Silicon Photonics for High-Performance Computing and Beyond. CRC Press, 2021, 177 -- 187 mehr… BibTeX

Konferenzbeiträge / Poster

- FAST: A Fast Automatic Sweeping Topology Customization Method for Application-Specific Wavelength-Routed Optical NoCs. Design, Automation and Test in Europe (DATE), 2021 mehr… BibTeX Volltext (mediaTUM)

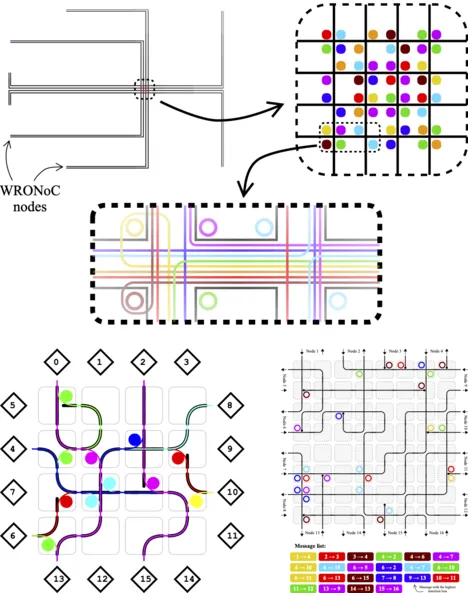

- ToPro: A Topology Projector and Waveguide Router for Wavelength-Routed Optical Networks-on-Chip. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2021 mehr… BibTeX Volltext (mediaTUM)

- Light: A Scalable and Efficient Wavelength-Routed Optical Networks-On-Chip Topology. IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC), 2021 mehr… BibTeX Volltext (mediaTUM)

2020

Zeitschriftenartikel

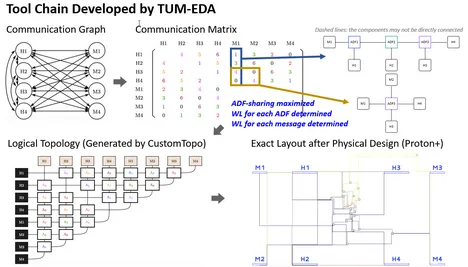

- PSION+: Combining logical topology and physical layout optimization for Wavelength-Routed ONoCs. IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, 2020 mehr… BibTeX Volltext ( DOI ) Volltext (mediaTUM)

Konferenzbeiträge / Poster

- Maximizing the Communication Parallelism for Wavelength-Routed Optical Networks-on-Chips. IEEE/ACM Asia and South Pacific Design Automation Conference (ASP-DAC), 2020 mehr… BibTeX Volltext (mediaTUM)

- PSION 2: Optimizing Physical Layout of Wavelength-Routed ONoCs for Laser Power Reduction. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2020 mehr… BibTeX Volltext (mediaTUM)

2019

Konferenzbeiträge / Poster

- PSION: Combining logical topology and physical layout optimization for Wavelength-Routed ONoCs. ACM/SIGDA International Symposium on Physical Design (ISPD), 2019 mehr… BibTeX Volltext (mediaTUM)

- Wavelength-Routed Optical NoCs: Design and EDA — State of the Art and Future Directions. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2019 mehr… BibTeX Volltext (mediaTUM)

2018

Konferenzbeiträge / Poster

- CustomTopo: A Topology Generation Method for Application-Specific Wavelength-Routed Optical NoCs. IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2018 mehr… BibTeX Volltext (mediaTUM)