Timing of Digital Circuits

Statistical Timing Analysis

Because of process variations and correlations the best-/worst-case approach will lead to very pessimistic analysis results and therefore to an immense gap between the performance predicted by EDA tools and the final silicon performance - industrial experience has shown that this gap can be up to 30% . A new timing analysis method which can reduce this gap is the so-called statistical analysis. In statistical analysis the gate delays and arrival times are represented by random variables which reflect the statistical variation of process parameters in silicon.

Aging-Aware Timing Analysis

In statistical analysis a distribution is given for all process parameters (e.g. gate oxide thickness). In contrast to that in aging analysis you have a directed drift of transistor parameters (e.g. threshold voltage) which depends on stress factors (e.g. temperature, supply voltage, workload, ...) over lifetime. When you look at it in more detail the drift is also a distribution and not a deterministic value.

Basically, the aging analysis consists of the following two steps. First, the stress factors for the circuit have to be determined. Second, the aged circuit performances have to be calculated with the help of a gate model that incorporates the aged gate performances caused by aging effects.

Waveform-Aware Timing Analysis

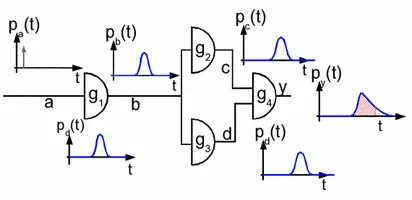

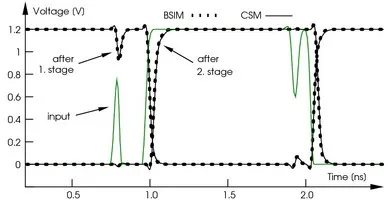

Timing validation is a crucial part in the design closure of digital circuits. The huge number of instances demands for abstract signal and delay models. Usually, logic signals are modeled as linear ramps with arrival and transition times. Nonetheless, real signals do not look like this. They shoot beyond the logic levels, have long transition tails, and are corrupted by interfering noise or radiation impacts.

To account for the real shape of the waveform more accurate models are required. Current Source Models are such kind of new model and can handle arbitrary signals and loads. The research focuses on efficient methods of deriving the models and their application in waveform aware timing analysis.