Theses and Student Jobs (HiWi)

The following list is by no means exhaustive or complete. Feel free to contact the members of the chair!

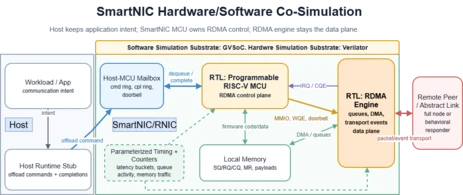

Programmable SmartNICs are becoming a key building block in modern data-center and edge systems, where network performance increasingly depends not only on raw link bandwidth but also on the coordination between embedded processors and specialized hardware datapaths. A typical SmartNIC integrates vendor-specific closed MCU or ARM control cores, DMA engines, queue managers, memory subsystems, RDMA/NIC logic, and packet-processing pipelines on a single device. These components do not operate in isolation: control software configures queues and descriptors, DMA engines move data between host and device memory, RDMA logic enforces protocol semantics, and packet pipelines process traffic at high speed. As a result, SmartNIC behavior emerges from tightly coupled hardware/software interactions inside the device.

However, existing evaluation tools do not fully capture this internal complexity. System-level frameworks are well-suited for composing hosts, devices, and networks, while RTL and FPGA prototypes provide detailed hardware validation at a much higher development cost. Between these two extremes, there is a need for a timing-aware SmartNIC-internal co-simulation platform that can execute realistic control software while exposing architectural effects such as queue contention, DMA latency, memory bottlenecks, RDMA scheduling behavior, and datapath/control-path interactions.

This project introduces \framework, a GVSoC-based virtual platform for co-simulation of SmartNIC hardware and software. We are interested in modeling SmartNIC as a heterogeneous system composed of programmable RISC-V control cores, memory and queue subsystems, DMA engines, RDMA/NIC hardware blocks, and packet I/O paths.

Requirements: Master students with proficiency in C++/Python, SystemVerilog, Verilator, Xilinx FPGA HLS/BD.

RISC-V's openness, flexibility, and innovation drive the study and research of the RISC-V Instruction Set Architecture (ISA) within simulators such as gem5 or QEMU. Being an open-source ISA, RISC-V allows researchers, developers, and students to explore and innovate in processor design without the constraints of proprietary ISAs. Simulators facilitate this exploration by providing a platform for modelling, simulating, and evaluating architectural changes and their impacts on performance and power consumption without physical hardware. This setup is invaluable for educational purposes, enabling hands-on learning experiences in computer architecture and hardware-software co-design, where processor and software systems are optimized together. Furthermore, simulators support cross-platform development, virtualization, and the detailed analysis needed for performance optimization, contributing to the growth of the RISC-V ecosystem. The combination of RISC-V's openness and the comprehensive simulation tools accelerates the development, testing, and deployment of RISC-V-based systems across various applications, from embedded systems to high-performance computing, making it fertile ground for innovation and education in computer systems design.

The contents of this project/thesis are as follows:

- Literature research on:

- RISC-V ISA and the ecosystem (i.e., build tools and existing versions),

- At least one simulation framework and the compatibility for RISC-V,

- Related works and the- state-of-the-art method.

- Develop a simple baseline model, i.e., implementing a system-level ISA simulation without any support of interrupts or peripherals.

- Implementation of an interface that enables customized instructions.

- Complete testing of the full system simulation of the standard ISA.

- Evaluation of the simulation firmware:

- Find suitable benchmarks with appropriate criteria of selection,

- illustrate the performance of the simulation tool (cycles per instruction, CPU run-time, coverage of the ISA, etc).

- Document all your findings and results.

- Optional:

- Develop an extension of the baseline model that enables interrupts and basic peripherals (UART, I2C),

- Comparison of the simulator to a real RISC-V core and try to calibrate the simulation,

- Customized instructions.

Prerequisites:

- Fundamentals about computer architecture and RISC-V

- C++/Python